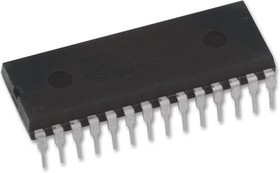

7204L12TPG, ASYNC, FIFO, 50MHZ, THIN DIP-28

Изображения служат только для ознакомления,

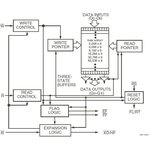

см. техническую документацию

см. техническую документацию

4 шт., срок 8-10 недель

6 260 руб.

Добавить в корзину 1 шт.

на сумму 6 260 руб.

Альтернативные предложения1

Описание

Полупроводники - Микросхемы\Логика\Устройства FIFO

The Renesas Electronics FIFO memory that loads and empties data on a first-in/first-out basis. The device uses Full and Empty flags to prevent data overflow and underflow.

Технические параметры

| Время Доступа | 12нс |

| Количество Выводов | 28вывод(-ов) |

| Максимальная Рабочая Температура | 70°C |

| Максимальное Напряжение Питания | 5.5В |

| Минимальная Рабочая Температура | 0°C |

| Минимальное Напряжение Питания | 4.5В |

| Организация Памяти | 4К x 9бит |

| Стиль Корпуса Микросхемы Логики | DIP |

| Функция FIFO | Асинхронный |

| Частота | 50МГц |

| Access Time | 12 ns |

| Bus Directional | Bi-Directional |

| Organisation | 4.096x9 |

Техническая документация

Дополнительная информация

Калькуляторы группы «Логические - FIFO память»

Типы корпусов импортных микросхем

Сроки доставки

Выберите регион, чтобы увидеть способы получения товара.